# Green-Power PWM Controller

#### **Features**

- Low Cost, Green-Power Burst-Mode PWM

- Very Low Start-up Current ( about 6μA)

- Low Operating Current ( about 3mA)

- Current Mode Operation

- Under Voltage Lockout (UVLO)

- VDD Over Voltage Protection(OVP)

- programmable over-temperature protection

- Internal Latch Circuit(OTP,OVP)

- Built-in soft start with 1ms

- Built-in Frequency jitter for better EMI Signature

- Soft Clamped gate output voltage 16.5V

- VDD over voltage protect 25.5V

- Cycle-by-cycle current limiting

- Sense Fault Protection

- Output SCP (Short circuit Protection)

- Built-in Synchronized Slope Compensation

- Leading-edge blanking on Sense input

- Programmable PWM Frequency

- High-Voltage CMOS Process with ESD

- DIP-8 & SOP-8 Pb-Free Package

- Compatible with SG6842J&LD7552

### **Applications**

- Power Adaptor

- Battery Charger Adapter

- Open Frame Switching Power Supply

- LCD Monitor

#### **General Description**

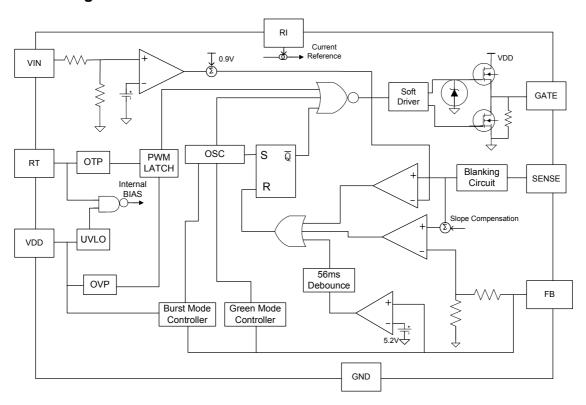

The CR6842 is a low startup current , low cost, current mode PWM controller with Green-Power & burst-mode power-saving operation. The integrated functions such as the leading-edge blanking of the current sensing, internal slope compensation provide the users a high efficiency, low external component counts, and low cost solution for AC/DC power applications. The special Green-Power function provides off-time modulation to linearly decrease the switching frequency under light-load conditions. And under zero-load conditions, the power supply enters burst-mode to further reduce power consumption by

shutting off PWM output. When the output of power supply is short or over loaded, the FB voltage will increase ,and if the FB voltage is higher than 5.2V for longer than 56msec the PWM output will be turned off. A external NTC resistor connected from pin RT to ground can be applied to over-temperature protection. Pulse by pulse current limit ensures a constant output current even under short circuit. PWM output will be disabled as long as VDD exceeds a threshold. When internal latch circuit is used to latch-off the controller, the latch will be reset when the power supply VDD is disabled.

Aug.2006 V 1.1 1/4

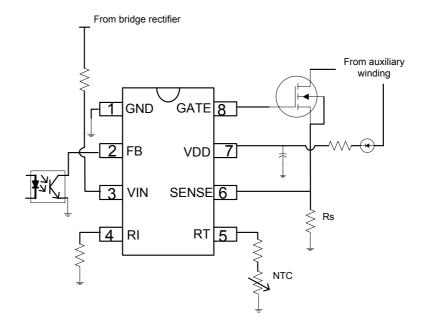

## **Pin Assignment & Description**

| Name  | Description                                                                                                                                                                                                   |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GND   | GND Pin                                                                                                                                                                                                       |  |  |  |  |

| FB    | Voltage feedback pin. The PWM duty cycle is determined by FB and Sense.                                                                                                                                       |  |  |  |  |

| VIN   | This pin is pulled high to the rectified line input through a large resistor for start-up. This pin is also used to detect line voltage to compensate for constant output power limit for universal AC input. |  |  |  |  |

| RI    | By connecting a resistor to ground to set the switching freq Increasing the resistor will reduce the switching freq                                                                                           |  |  |  |  |

| RT    | An NTC resistor is connected from this pin to ground for over-temperature protection.                                                                                                                         |  |  |  |  |

| SENSE | Current sense pin, The sensed voltage is used for current-mode control and pulse-by-pulse current limiting.                                                                                                   |  |  |  |  |

| VDD   | Power supply voltage pin.                                                                                                                                                                                     |  |  |  |  |

| GATE  | Gate drive output to drive the external MOSFET.A soft driving waveform is implemented to improve EMI.                                                                                                         |  |  |  |  |

# **Typical Application Circuit**

Aug.2006 V 1.1 2/4

# **Block Diagram**

### **Absolute Maximum Ratings**

| Symbol             | Parameter                     | Rating       | Unit         |  |

|--------------------|-------------------------------|--------------|--------------|--|

| $V_{\mathrm{DD}}$  | Supply voltage Pin Voltage    | 40           | V            |  |

| $V_{FB}$           | Input Voltage to FB Pin       | -0.3 to 6V   | V            |  |

| V <sub>Sense</sub> | Input Voltage to SENSE Pin    | -0.3 to 6V   | V            |  |

| $P_{\mathrm{D}}$   | Power Dissipation             | 1000         | mW           |  |

|                    | ESD Capability, HBM Model     | 2000         | V            |  |

|                    | ESD Capability, Machine Model | 200          | V            |  |

| $T_{ m L}$         | Lead Temperature(Soldering)   | DIP-8(10sec) | 260          |  |

| $T_{STG}$          | Storage Temperature Range     |              | -55 to + 150 |  |

**Electrical Characteristics (** $Ta=27^{\circ}C$  unless otherwise noted,  $V_{DD}=15V$ .)

| Symbol                 | I Characteristics (Ta=27°C                       | Conditions                                    | Min.  | Typ.  | Max.  | Unit           |

|------------------------|--------------------------------------------------|-----------------------------------------------|-------|-------|-------|----------------|

|                        | Itage (V <sub>DD</sub> Pin)                      | Gorialione                                    |       | . yp. | Maxi  | Jine           |

| I <sub>ST</sub>        | Startup Current                                  | VDD=17                                        |       | 5.6   | 30    | μΑ             |

| I <sub>SS</sub>        | Operating Current                                | V <sub>FB</sub> = V <sub>SENSE</sub> = 0V     |       | 3.5   | 5     | mΑ             |

| V                      | Start Threshold Voltage                          | VDD=15                                        | 17.6  | 18.6  | 19.6  | V              |

| $V_{\text{TH(ON)}}$    | Min. Operating Voltage                           |                                               | 10.1  | 11.1  | 12.1  | V              |

| V TH(OFF)              | VDD Over Voltage                                 |                                               | 10.1  | 11.1  | 12.1  | <b>V</b>       |

| VDD-OVP                | Protection(Latch off)                            |                                               | 26.4  | 27.4  | 28.4  | V              |

| VDD-th-g               | VDD Low-Threshold Voltage to Exit Green-OFF Mode |                                               | 12    | 12.5  | 13    | V              |

| Voltage Fe             | edback (FB Pin)                                  |                                               |       | L     |       |                |

| I <sub>FB</sub>        | Short Circuit Current                            | V <sub>FB</sub> =0V                           |       |       | 1.5   | mA             |

| $V_{FB}$               | Open Loop Voltage                                | V <sub>FB</sub> =Open                         |       | 5.88  |       | V              |

| Current Se             | ensing (SEN Pin)                                 |                                               |       | L     |       |                |

| $V_{TH}$               | Threshold voltage for current limit              | I <sub>VIN</sub> =0                           |       | 0.66  | 0.9   | V              |

| T <sub>PD</sub>        | Delay to Output                                  |                                               |       | 100   | 200   | nsec           |

| Z <sub>CS</sub>        | Input Impedance                                  |                                               |       | 12    |       | ΚΩ             |

| B <sub>nk</sub>        | Leading Edge Blanking Time                       |                                               | 260   | 360   | 460   | nsec           |

| Oscillator             | (RI Pin)                                         | <u>l</u>                                      |       |       |       |                |

| Fosc                   | Frequency in nominal mode                        | RI=26KΩ                                       | 63    | 68    | 73    | KHz            |

| F <sub>OSC-green</sub> | Frequency in green mode                          | RI=26 KΩ                                      | 33.3  | 36    | 38.5  | KHz            |

| $V_N$                  | Beginning of frequency reducing at FB Voltage    | VDD=15V                                       | 1.9   | 2.1   | 2.3   | V              |

| $V_{G}$                | End of frequency reducing at FB voltage          | VDD=15V                                       | 1.4   | 1.6   | 1.8   | V <sub>G</sub> |

|                        | Frequency Temp. Stability                        | -30-85                                        |       | 5.0   |       | %              |

| GATE Driv              | e Output (GATE Pin)                              | L                                             |       |       |       |                |

| V <sub>OL</sub>        | Output Low Level                                 | V <sub>DD</sub> =12V,<br>I <sub>O</sub> =50mA |       |       | 1.6   | V              |

| V <sub>OH</sub>        | Output High Level                                | V <sub>DD</sub> =12V,<br>I <sub>O</sub> =50mA | 6.7   |       |       | V              |

| T <sub>R</sub>         | Rising Time                                      | VDD=15V,C <sub>L</sub> =1nF                   | 150   | 203   | 350   | ns             |

| T <sub>F</sub>         | Falling Time                                     | VDD=13V,C <sub>L</sub> =1nF                   | 30    | 74    | 90    | ns             |

| DC <sub>MAX</sub>      | Maximum Duty Cycle                               |                                               | 80    | 92    | 95    |                |

|                        | perature Protection Section                      | •                                             |       |       |       |                |

| I <sub>RT</sub>        | Output current of pin RT                         | RI=26KΩ                                       | 64    | 68    | 76    | μΑ             |

| $V_{\text{OTP}}$       | Threshold voltage for over-tem                   | perature protection.                          | 1.015 | 1.053 | 1.115 | V              |

| RI Section             |                                                  |                                               |       | •     |       |                |

| RI <sub>NOR</sub>      | RI Operating Range                               |                                               | 15.5  |       | 36    | ΚΩ             |

| $RI_{MAX}$             | Max RI value for Protection                      |                                               |       | 216   |       | ΚΩ             |

| RI <sub>MIN</sub>      |                                                  |                                               |       | 6     |       | ΚΩ             |

Aug.2006 V 1.1 Chengdu Chip-Rail Tech.Co.,Ltd 4/4